FPGA Four-Function Calculator

A basic four function calculator implemented using Verilog capable of four-bit addition, subtraction, multiplication, and division, with a seven-segment display output and inputs for digits and operations.

Duration

3 weeks

Team Size

2 members

Overview

This was a final project for my ECE2029 Introduction to Digital Circuit Design course, where we designed and implemented a four-function calculator on an FPGA using Verilog. The calculator supports addition, subtraction, multiplication, and division of two four-bit numbers, with results displayed on a seven-segment display. We implemented the arithmetic logic units for each operation, as well as the necessary control logic to handle user inputs and display outputs.

Technical Approach

The major aspects of the project are described below including input, all math modules, and outputs.

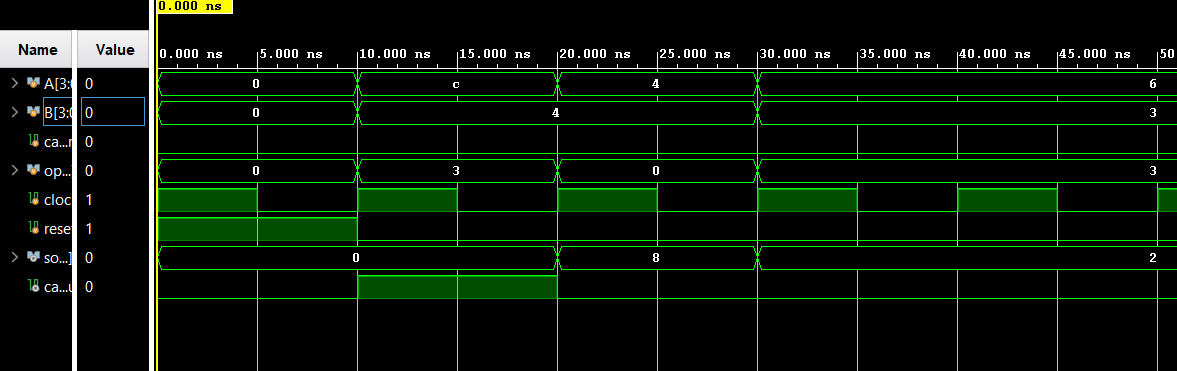

- Inputs: This calculator took in 3-4 inputs. A calibration input (HIGH) would reset all values in the calculator to zero; this input is optional and defaults to LOW. It took in two four-bit numbers in binary to be operated on by the calculator, and one operation input which could either be 00, 01, 11, or 10 for addition, subtraction, multiplication, and dvision respectively.

- Addition, Subtraction, and Multiplication: The addition, subtration, and multiplication modules were all implemented using full adder modules. Addition and subtraction used the same module, having a flag bit which when HIGH, would trigger subtration. The full adder would act as normal for addition, and for subtraction would use two's compliment. The multiplication module was implemented finding partial products with AND gates, being summed at the end with a full adder.

- Division: The division module was implemented using a restoring division algorithm, which iteratively subtracts the divisor from the dividend and shifts the quotient bits. Division is a complex operation requiring bit shifting logic and could not be implemented solely using basic logic gates.

- Display Output: The solution of each math operation is then fed to a display driver to convert it to display output. This was implemented by creating a seven-segment display driver, which converts the binary output of the arithmetic units into the appropriate segments to display the result. This would display the solution in decimal.

Results

Implementing all arithmetic operations was challenging, especially division. The calculator successfully performed all four operations with accurate results and display outputs.